Innovating with III-V's

Europe's Independent GaAs InP GaN MMIC Supplier

#### Mixed D/A ED02AH process for radar control functions and new GaN/Si for hyper-frequency power applications

Innovating with III-V's

3

#### **Europe's Independant IIIV Full-Service Foundry**

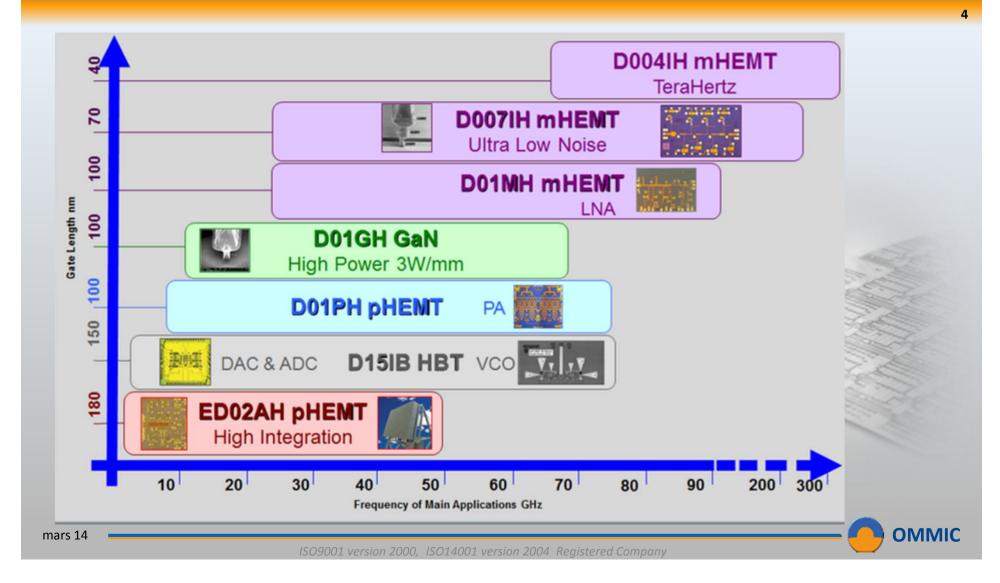

# **OMMIC PROCESS**

# OMMIC ED02AH D/A mixed process for control functions

SO9001 version 2000, ISO14001 version 2004 Registered Company

#### Introduction

•III/V provide optimum trade-offs in terms NF, gain, power and linearity for various applications including wireless telecommunication infrastructure, security scanners, radars and instrumentation.

•A weaker feature of III/V technologies  $\rightarrow$  limited level of integration.

We will show how E/D PHEMT processes enable the integration of analogue functions like phase shifters and attenuators with serial to parallel converters

$E/D \rightarrow Serial ctrl \rightarrow High integration \rightarrow cost reduction$

All integrated on the same chip to achieve state of the art performance through the example of Corechips.

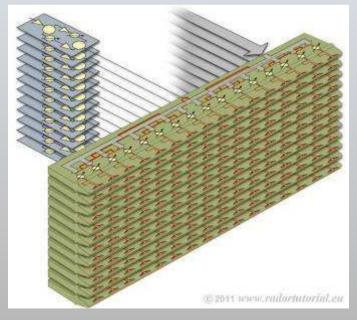

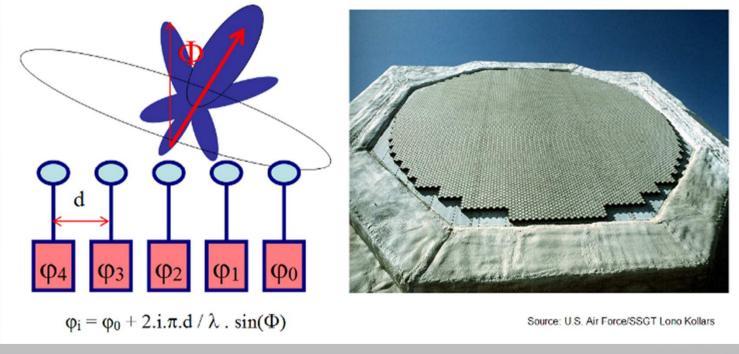

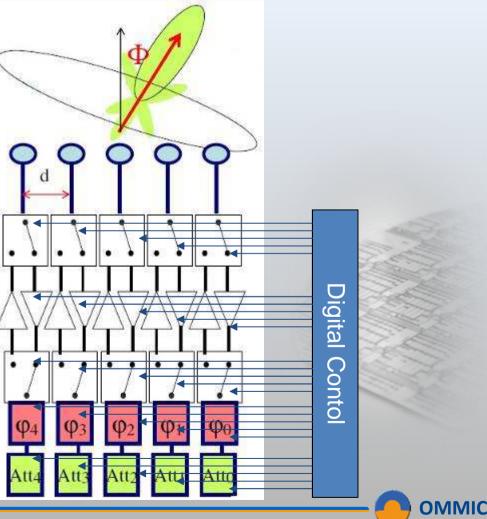

#### **Electonically steerable antenna example**

The orientation of the beam is obtained by the use of variable phase shifters attached to each radiating element

The side lobes may then be controlled by variable attenuators attached to each element

#### **Electonically steerable antenna example**

Each antenna element may contain :

•A variable phase shifter

•A variable attenuator

•Switches, to be able to use the same system in receive or transmit modes •Amplifiers:

to compensate the losses and create some gain,

to reduce the noise in receive mode, to create enough power to drive power amplifiers in transmit mode

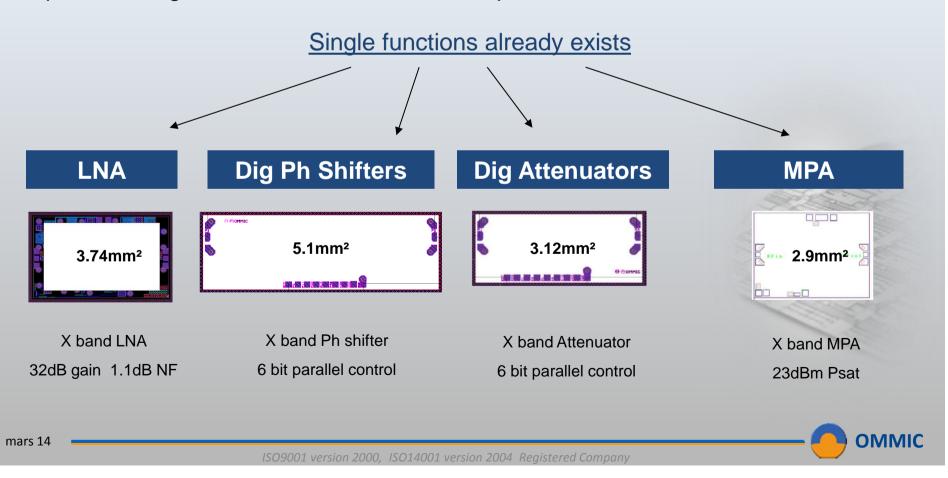

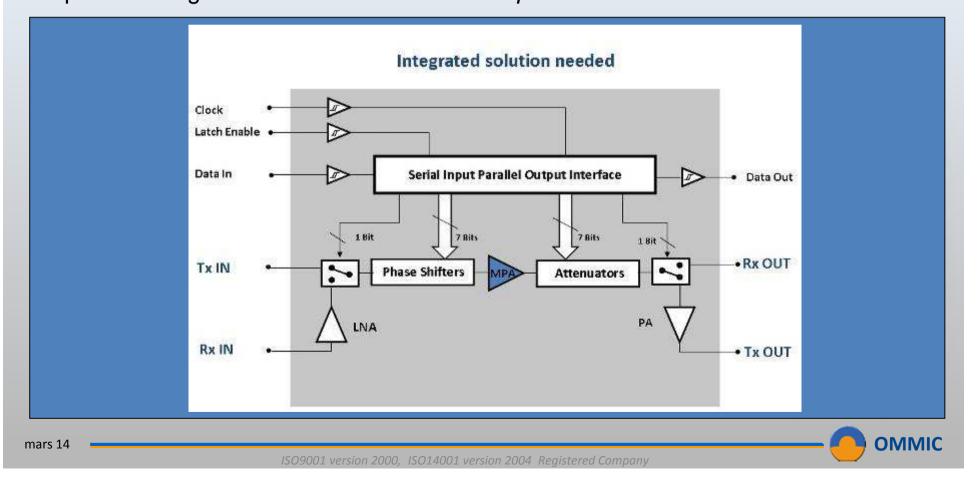

#### From single function to multiple function chip

Due to higher frequency of radar application, integration of functions become a key aspect of designs. *Below is the X band example*

#### **Serial Interface need : 6 bit corechip example**

#### From single function to multiple function chip

Due to higher frequency of radar application, integration of functions become a key aspect of designs. *Below is the X band example*

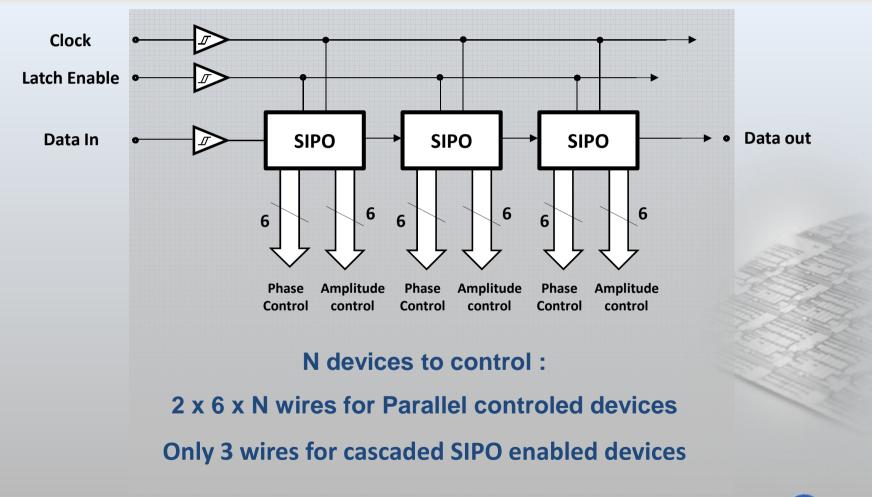

#### **Multiple Cascaded devices : The SIPO Advantage**

#### How to realize the SIPO

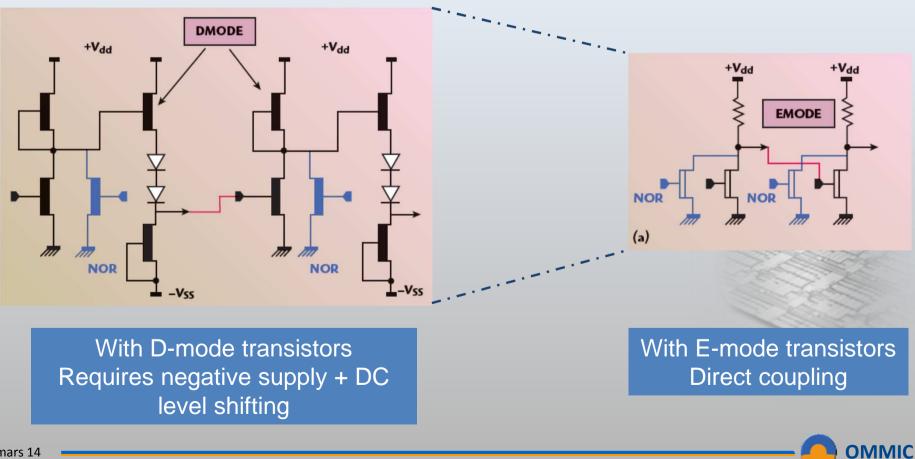

#### Efficient SIPO on chip requires Enhancement mode process

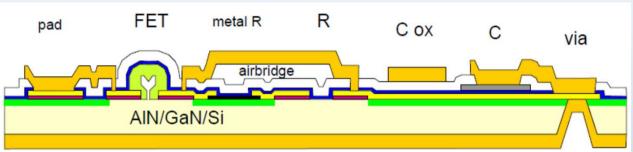

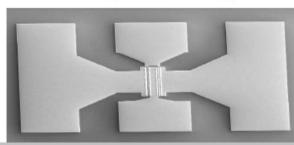

#### **OMMIC E/D process : ED02AH**

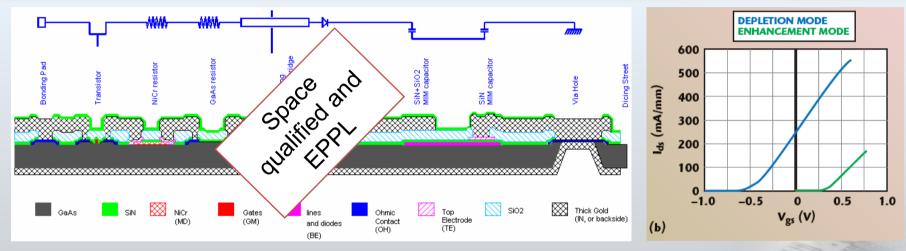

•Hetero-epitaxy with a pseudomorphic (GaInAs) active layer

- •0.18µm gate length (60 GHz Ft)

- •Depletion and Enhancement mode recessed transistors: Vt=0.225V or -0.9V

- •2 types of diodes (0.18µm "GM" and 3µm "BE") for mixing, level shifting, or varactors.

- •3 types of Resistors : 40, 200 or 500 Ohms.square

- •2 types of MIM Capacitors : 50 or 400 pF/mm2

- •Full SiN + SiO2 + SiN protection ensuring high reliability

- •SiO2/SiN + air bridge isolation between layers to reduce the parasitic capacitances.

- $\bullet 1.25 \mu m$  or 2.5  $\mu m$  thick gold metallisation for interconnections and spiral inductors.

- •Via holes through the 100µm substrate to reduce parasitic inductances to ground.

#### **Examples of SIPOs**

Mumber of

Number of transistor gates

| Number of<br>control bits | Number of transistor gates | Global DC consumption<br>including drivers and latches |

|---------------------------|----------------------------|--------------------------------------------------------|

| 12                        | 700 (58 / bit)             | 150 mW (13 mW / bit)                                   |

| 26                        | 1500 (58 / bit)            | 350 mW (13 mW / bit)                                   |

| 18                        | 1500 (83 / bit)            | 300 mW (17 mW / bit)                                   |

| 24                        | 1500 (63 / bit)            | 200 mW (8 mW / bit)                                    |

| 26                        | 1200 (46 / bit)            | 60 mW (2.3 mW / bit)                                   |

| 10                        | 800 (80 / bit)             | 4 mW (0.3 mW / bit) Low speed                          |

омміс

15

ISO9001 version 2000, ISO14001 version 2004 Registered Company

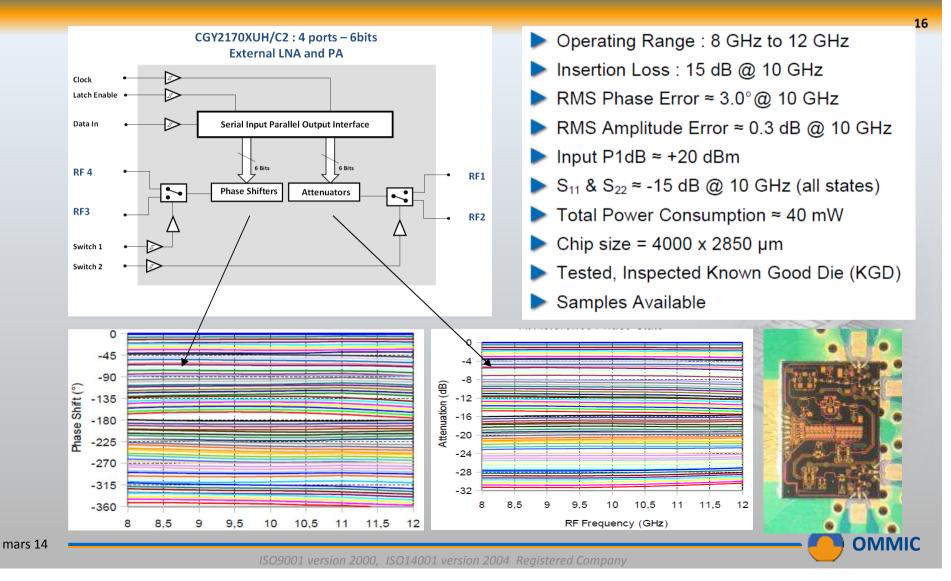

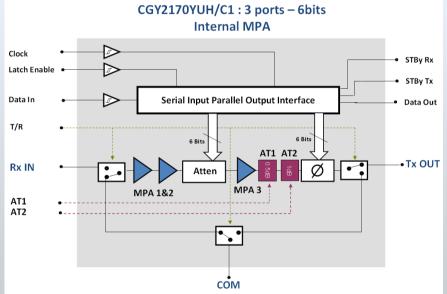

#### **Examples of X band Corechips**

#### **Examples of X band Corechips**

Separated register for Rx and Tx External additional attenuators Operating Range : 8 GHz to 12 GHz Gain Tx/Rx : 6 dB @ 10 GHz RMS Phase Error ≈ 3.0° at 9-10 GHz RMS Amplitude Error ≈ 0.4 dB from 8-11 GHz Output P1dB Tx ≈ +11 dBm Output P1dB Rx ≈ +11 dBm S<sub>11</sub> & S<sub>22</sub> < -17 dB @ 10 GHz (all states)</p> Total Power Consumption ≈ 0,36 W Chip size = 4700 x 3800 µm Tested, Inspected Known Good Die (KGD) Samples Available **OMMIC**

SO9001 version 2000, ISO14001 version 2004 Registered Company

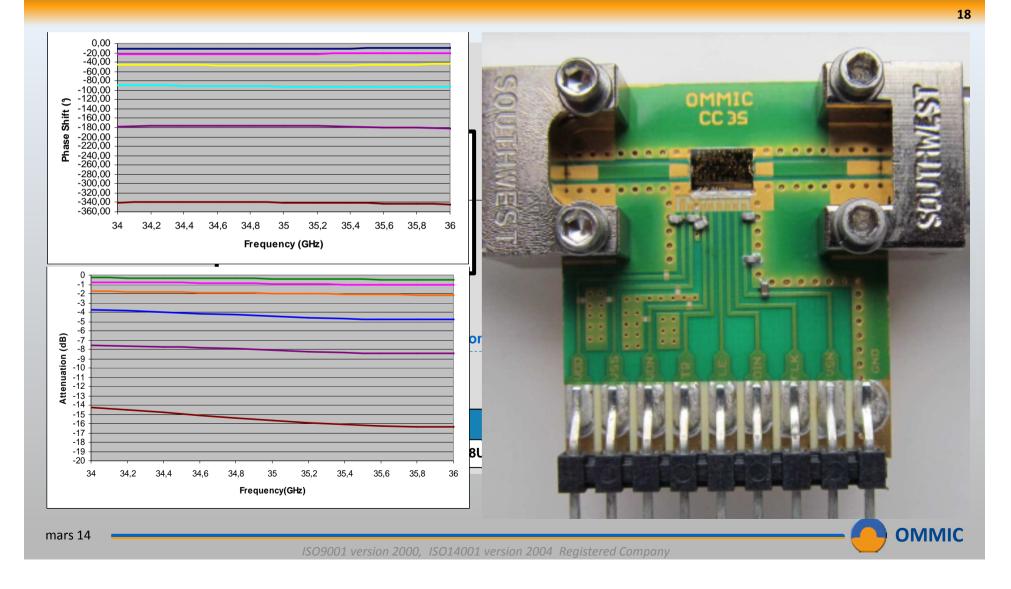

#### Nowadays brand new 35GHz Corechip

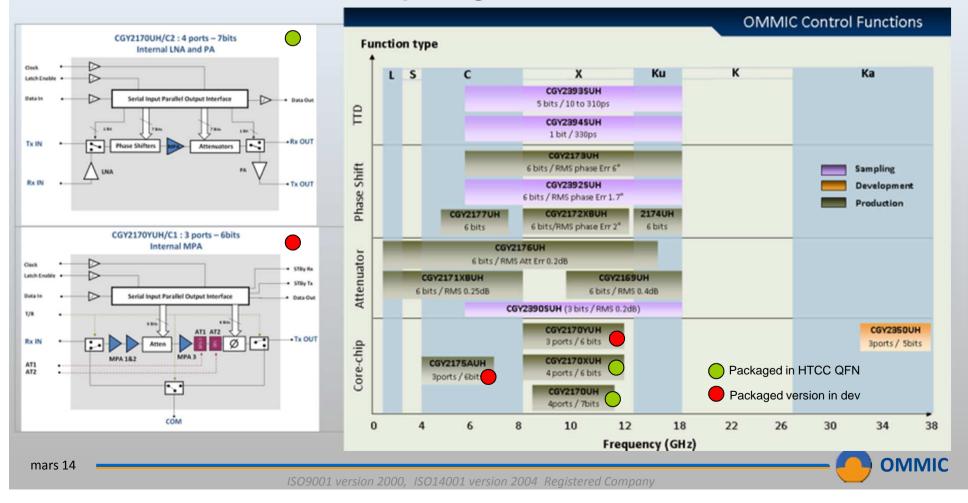

# **OMMIC** Corechip offer

- More than 15 Core chip in production from C band to Ka Band

- More than 40 Custom Corchip designed for customers

Innovating with III-V's

#### future control function

For the Development of Core Chips including SIPO above 60 GHz, a new process is required.

OMMIC has thus developed a true Emode 0.1um process using a metamorphic layer

- 200 GHz Ft, 300 GHz Fmax

- => E band Core Chip possible

- 4 15 dB MSG @ 30 GHz

- E-mode => easy SIPO

- Large Vg swing => switches

- Same passives than ED02AH

10 Number of devices -150 -100-50 50 100 150 200 250 300 350 400 Vt (mV) (a) G<sub>m</sub>(DC) at Vgs=0.5, and Vds=1V UCL=1,41392 0.8 LCL=0.86064 Average = 1137 mS/mm,  $\sigma$  = 94 mS/mm Gate voltage swin; UCL=0.6993 CEN=0.62112 LCL=0.54 0.5 Average = 0.62V,  $\sigma = 27mV$

11

OMMIC

# OMMIC GaN / Si

509001 version 2000, ISO14001 version 2004 Registered Company

Innovating with III-V's

# mmW GaN HEMT on Si : Goal

# The choice of a GaN heterostructure on Si is dictated by the following points:

- Increase power density 3 times the current GaAs technology

- Address applications up to 20W, compatible with the Si Thermal conductance, primarily targeting frequency bands from 15 GHz and 100 GHz.

- Access to the epitaxial material without depending on SiC sources

- Full replacement of GaAs processes for professional applications up to 100GHz at a lower cost/mm2

## mmW GaN HEMT on Si

509001 version 2000, ISO14001 version 2004 Registered Compan

Innovating with III-V's

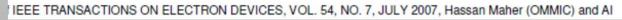

## Advanced release of GaN/Si process

#### Preliminary Design Kit available under ADS or AWR

**D01GH**:

- ▶Idss ( 0V) = 650 mA/mm ▶Vt= - 1.5V

- ▶Gm max ext= 600 mS/mm

- Ft= 100 GHz, Fmax =180 GHz @ Vds = 3 V

- ▶ MSG = 14 dB @ 30 GHz

- Vbgd min =30V, typical = 40V (Vds max= 24V)

- ▶ Vdd =15V

- Psat> 2.5 W/mm at 30 GHz (Vds =15V)

Applications :

- High frequency Power Amplifiers 10GHz to 94 GHz

- Robust Low Noise Amplifiers (< 20 GHz)

- Robust Control Functions

- High Linearity Mixers

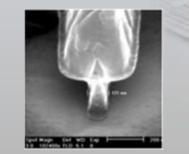

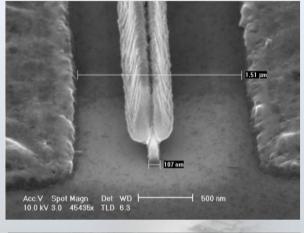

0.11 µm gate (GaN on Si)

**OMMIC**

24

mars 14

O9001 version 2000, ISO14001 version 2004 Registered Company

### **D01GH Key power applications and targets**

- Scaled GaN /Si ( 30% shorter gate) can replace GaAs and InP for power applications with following power capability :

- 1 W @ 94GHz

- 6 W @ 45GHz

- 12 W @ 30GHz

- 25 W @ 10GHz

- 3 KEY features are required :

- In situ SiN passivation (reduced lag effects in planar structure)

- Si substrate with proprietary buffer and extension to 6 inch

- Regrown ohmics (for high gm and low noise)

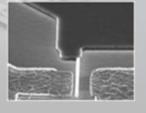

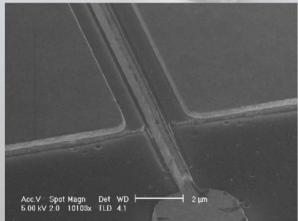

# **D01GH PROCESS FLOW**

- •European epi ( EPIGaN)

- •Regrown ohmics (for high gm)

- •Mushroom gate (100nm, 60nm)

- In situ SiN passivation (for low lag effects <10%)</li>

2x70um HEMT

#### Thank you for your attention